这是本文档旧的修订版!

PCIe

PCIe标准由PCIe-SIG组织负责,网站https://pcisig.com/,网站上的specification需要成为PCIe-SIG组织成员才能下载,普通用户无法下载。

常用标准

如下标准包括了PCIe 1.0 ~ 6.0.

版本差异

PCIe 1.0至5.0,速率的提升依赖于时钟频率的成倍提升,但到了PCIe 6.0,时钟频率和5.0一致,速率提升主要是用了高阶的调制PAM4。

各版本的具体差异见下表:

| Data Rate 单向 | Unit Interval | Modulation | Encoding | Effective Data Rate | Base Specification Revision | 示波器要求 Tx 测试 |

||||||

| 6.x | 5.x | 4.x | 3.0 | 2.0 | 1.0 | 带宽 | 最小采样率 | |||||

| 2.5GT/s | 400ps | NRZ | 8b/10b | 2Gbit/s | ✓ | ✓ | ✓ | ✓ | ✓ | ✓ | 6 GHz | 20 GSa/s |

| 5.0GT/s | 200ps | NRZ | 8b/10b | 4Gbit/s | ✓ | ✓ | ✓ | ✓ | ✓ | 12 GHz | 40 GSa/s | |

| 8.0GT/s | 125ps | NRZ | 128b/130b | ~8Gbit/s | ✓ | ✓ | ✓ | ✓ | 12 GHz | 40 GSa/s | ||

| 16.0GT/s | 62.5ps | NRZ | 128b/130b | ~16Gbit/s | ✓ | ✓ | ✓ | 25 GHz | 80 GSa/s | |||

| 32.0GT/s | 31.25ps | NRZ | 128b/130b | ~32Gbit/s | ✓ | ✓ | 50 GHz 33GHz for CEM | 80 GSa/s | ||||

| 64.0GT/s | 31.25ps | PAM4 | 1b/1b | 64Gbit/s | ✓ | 50 GHz 33GHz for CEM | 80 GSa/s | |||||

| 参考文献: 1、PCI Express® Base Specification Revision 6.0 Table 1-1 PCIe Signaling Characteristics Table 8-6 Data Rate Dependent Transmitter Parameters 8.4.2.1 Procedure for Calibrating a Stressed EH/EW Eye 2、Keysight: D9050PCIC PCIe 5.0 TX Compliance Test Software.pdf |

||||||||||||

设计要求

| Parameters of PCIe® Standard | |

| Parameter | Value |

| Data Clock Frequency | PCIe® Gen 1: 1.25 GHz (2.5 Gbps) |

| PCIe® Gen 2: 2.5 GHz ( 5 Gbps) | |

| PCIe® Gen 3: 4 GHz (8 Gbps) | |

| PCIe® Gen 4: 8 GHz (16 Gbps) | |

| AC Coupling Capacitors | AC capacitors required:75 nF–220 nF |

| Polarity Reversal | Allowed |

| Max Intra-Pair Skew | 5 mils |

| Max Inter-Pair Skew | No Inter-pair specification |

| Trace Impedance | PCIe® Gen 1 and 2:100 Ω ±5% differential; 50 Ω ±5% single ended |

| PCIe® Gen 3 and 4: 85 Ω ±5% differential; 42.5 Ω ±5% single ended | |

| 参考文献: TI Layout Guidelines of PCIe® Gen 4.0 Application With the TMUXHS4412 Multiplexer.pdf | |

测试

PCIe总线除了有Base Spec,还有关于PCIe卡的Spec(又称为CEM Spec,全称为PCI Express Card Electromechanical Specification)。PCIe On-Board连接的测试适用于Base Spec,而带有PCIe卡连接器的则适用CEM Spec1)。

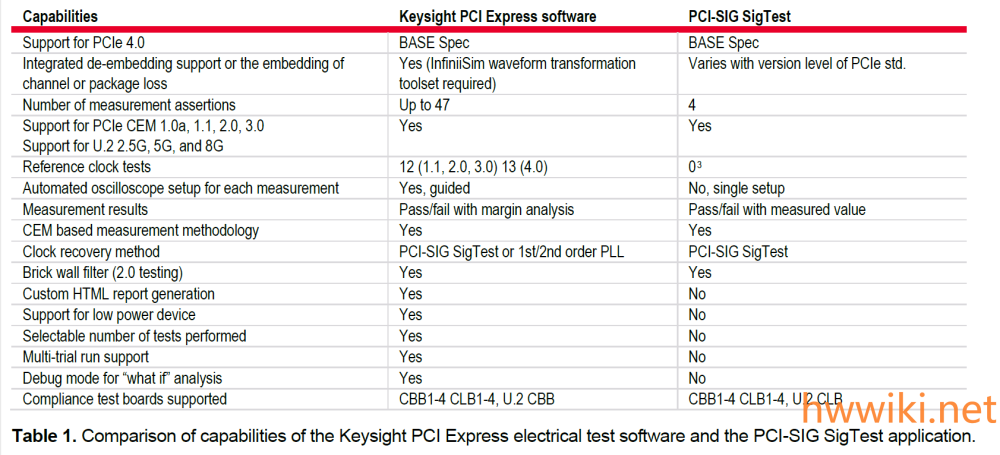

测试软件有两种,一种是有PCI标准组织提供的免费软件PCI-SIG SigTest,另一种是各仪器厂家推出的付费软件如Keysight PCI Express software。以PCIe 4.0为例,两者的对比如下,PCI-SIG SigTest免费,但功能少2) 。

是德科技(KEYSIGHT)PCIe测试方案介绍见网址PCIe,微信公众号文章如下:

干货:PCIE6.0技术剖析

干货 | PCIe 5.0最新更新及测试挑战

具体的测试操作见如下文档:

Tx测试:D9050PCIC-PCIeGen5-Test-Software-MOI-latest

RX测试:N5991 Receiver Compliance Test Automation Platform

互联测试:How to Ensure Interoperability and Compliance of USB Type-C Cables and Connectors

调试案例

介绍

如下内容大部分来源于Felix的博客文章PCIe扫盲系列博文连载。

拓扑结构

结构中有三个角色,RC(Root Complex)、EP(EndPoint)和Swtich,三者之间的关系如下图3)。RC相当于主设备,EP相当于从设备。

Lane

PCIe收发链路可以有多条Lane组成,配置有x1 x2 x4 x8 x16 x32,Lane越多速率越快,如x2的速率是x1的两倍。4)

差分信号的Vpp大约为800mV,单端D+ D-大约为400mV5)。

PCIe x1 Lane电路如下图,Rx差分对(PCIE_RX_P PCIE_RX_M)和Tx差分对(PCIE_TX_P PCIE_TX_M)组成了一组Lane。

链路初始化与训练

PCIe总线中的链路初始化与训练(Link Initialization & Training)是一种完全由硬件实现的功能,处于PCIe体系结构中的物理层。整个过程由链路训练状态机(Link Training and Status State Machine,LTSSM)自动完成6)。

在系统复位后,会自动进行链路训练,以达成以下目标:位锁定(Bit Lock)、字符锁定(Symbol Lock,Gen1 & Gen2 Only)、块锁定(Block Lock,Gen3 Only)、确定链路宽度(Link Width)、通道位置翻转(Lane Reversal)、信号极性翻转(Polarity Inversion)、确定链路的数据率(Data Rate)和通道对齐(Lane-to-Lane De-skew)等功能。

链路训练状态机LTSSM有11个状态(其中又有多个子状态),分别是Detect(根据RC时间常数来判断Rx端是否存在7))、Polling、Configuration、Recovery,L0、L0s、L1、L2(L3是可选的)、Hot Reset、Loopback和Disable状态。系统进行复位操作(Cold, Hot or Warm Reset)后,会自动进入Detect状态8)。

各状态之间的转换如下图所示:

参考时钟

参考时钟REFCLK是一种类LVDS信号(即Low Voltage Swing,Differential Clocks),时钟频率为100MHz,Gen1~4精度为±300ppm,Gen5为±100ppm。注意其和Data的时钟不同,其是固定的100MHz,而Data的时钟则是由CDR(Clock Data Recovery)电路直接从Data波形中恢复出来的,CDR电路需要此参考时钟。9) 10)。

REFCLK的电平如下图11):

PCIe参考时钟的三种架构12):

1、Common Refclk (Shared Refclk) Architecture

架构如下图,共用同一个时钟,PCIe spec推荐这种架构。

2、Data Clocked Rx Architecture

2、Data Clocked Rx Architecture

参考时钟直接从数据流中恢复出,这种难度大,对CDR的要求高。

3、Separate Refclk Architecture

收发双方用独立的时钟,PCIe spec强烈不推荐,不建议使用。

REFCLK标准参考“PCI Express® Base Specification Revision 6.0 : 8.6 Refclk Specifications”。

中断

有以下两种13),PCIe RC和对应的EP中断需要能支持相同的中断,否则有些功能会实现不了。

1、INTx14)

最早采用的基于边缘信号的INTx。

2、MSI/MSI-X15) 16)

后续的基于消息信号的MSI/MSI-X。

复位

有如下四种复位17)。

1、冷复位

因为主电源断开后重新连接导致的复位。PCIe Spec允许两种实现基本复位的方式。一是直接通过边带信号PERST#(PCI Express Reset);二是不使用边带信号PERST#,PCIe设备在主电源被切断时,自行产生一个复位信号。

2、暖复位

其是可选的,指的是在不关闭主电源的情况下,产生的复位。然而,PCIe Spec并未明确规定暖复位的产生机制,因此,如果产生暖复位完全是由系统设计者决定的。

3、热复位

其是一种In-band 复位,其并不使用边带信号。

如果Switch的Upstream端口收到了热复位,则会将其广播至所有的Downstream端口,并复位其自己。如果PCIe设备的Downstream端口接收到热复位,则只需要复位其自己即可。

当PCIe设备接收到热复位后,LTSSM会进入Recovery and Hot Reset状态,然后返回值Detect状态,并重新开始链路初始化训练。其该PCIe设备的所有状态机,硬件逻辑,端口状态和配置空间中的寄存器(除了Sticky bits)都将被初始化值默认状态。

4、功能复位18)

PCIe总线自V2.0加入了此功能。该功能主要针对的是支持多个功能的PCIe设备(Multi-Fun PCIe Device),可以实现只对特定的Function复位,而其他的Function不受影响。

此功能是可选的。

热插拔

PCIe总线的热插拔主要指的是PCIe卡设备的热插拔,以及相关的实现机制等19)。

PCIe卡有两个用于热插拔机制的引脚——PRSNT1#和PRSNT2#。PCIe卡设备上的这两个信号之间是短路的,PCIe插槽的PRSNT1#被固定地连接到地,PRSNT2#则被上拉。且PCIe卡上的这两个信号的金手指长度要比其他的信号的金手指长度要短一点。

如下图所示,当PCIe卡设备未被完全插入插槽时,插槽的PRSNT2#信号由于上拉的作用,将一直处于高点平状态。当PCIe卡设备被完全插入插槽后,插槽上的PRSNT2#信号则会被PCIe卡设备的短路线连接到地,从而使得其变为低电平。换句话说,从插槽的角度看,当PRSNT2#位高电平时,则认为PCIe卡设备未能正确插入或者无PCIe卡设备;当PRSNT2#位低电平时,表明PCIe卡设备被正确地插入插槽中。

评论